# Prototype Development of Silicon Array Sensor for X-ray Imaging

H. O. Kim<sup>a\*</sup>, H. J. Hyun<sup>a</sup>, D.H. Kah<sup>a</sup>, D.H. Son<sup>a</sup>, Y.I. Kim<sup>a</sup>, H. Park<sup>a</sup>, H.J. Kim<sup>a</sup> and H.D. Kang<sup>b</sup> <sup>a</sup>Basic Atomic Energy Research Institute, Kyungpook National Univ. Daegu 702-701, Korea <sup>b</sup>Radiation Science Research Institute, Kyungpook National Univ., Daegu 702-701, Korea email: hokim@knu.ac.kr

# 1. Introduction

Because X-ray radiation is absorbed at different rates in different tissue types, it is useful for medical diagnoses. The photographic plate has mainly been used to detect the radiation in medical imaging field. While it is sensitive to X-rays, it requires a lot of exposure.

In the silicon, X-ray photons are converted to electron-hole pairs which are collected to detect X-rays. A silicon sensor is sensitive and allows lower doses of X-rays. And besides, a silicon array sensor provides two-dimensional position information with a high resolution so that it has a wide range of applications: the detector for high energy and nuclear structure physics, fission fragments detection, room temperature X-ray detection, gamma transient detection and so on.

Our prototype for X-ray imaging consists of a silicon array sensor with single-sided 256 pixels and a front-end signal readout electronics in which 256 channels are taken as a serialized signal.

# 2. Silicon Array Sensor

. The silicon array sensor is fabricated on high resistivity(>  $5k\Omega cm$ ), <100>-oriented and n-type silicon wafers. The specification is shown in Table 1.

| Tuble 1 The specification of the smeon array sensor |                          |

|-----------------------------------------------------|--------------------------|

| high resistivity (>5kΩcm),                          | <100>,and n-type silicon |

| wafer                                               |                          |

| sensor area(µm <sup>2</sup> )                       | 200 x 200                |

| sensor thickness(µm)                                | 380                      |

| number of pixels                                    | 4 x 64                   |

$p^+$  implant area( $\mu m^2$ )

bonding pad size( $\mu m^2$ )

100 x 100

120 x 80

Table 1 The specification of the silicon array sensor

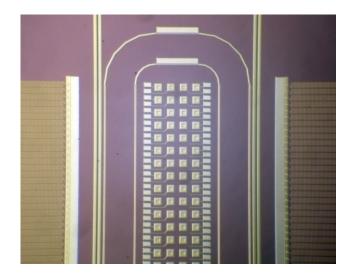

As shown in Fig. 1, the prototype sensor is made up 4 linear type arrays of 64  $p^+$  implant pixels and the bonding pads at the both edges are designed to read a signal out from each pixel. The RC chips are fabricated in outside of the pads to apply the reverse bias voltage and read sensor signals out from the pixels. The opposite of the pixel side is plate implanted for n

When charged particles pass through silicon pixels, which are fully depleted by applied reverse bias voltage, electron-hole pairs are produced[1]. The hole carriers are collected in  $p^+$  doped regions of pixels on which the

aluminum metals deliver to readout electronics system through the pixel pads and RC chips. Each RC chip is connected to readout system for 128 pixel output signals. The pixel sensor is fully depleted above 35V so that we adopt 60V as the reverse bias voltage in which the leakage current is less than 1.7 nA at 70V

Fig 1. A photo of a fabricated silicon array sensor

### 3. Front-end Electronics

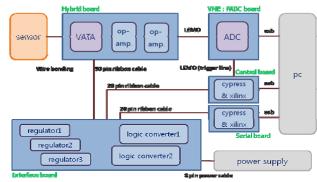

The readout electronics consists of a VA Hybrid, a VA Interface, a control board, a serial board and a Flash ADC as in Fig.2.

Fig. 2. Schematic diagrams of readout electronics.

Analog signals from the silicon pixel array sensor are processed by VA Hybrid board. On VA Hybrid, each of two VATA chips[2] holds all 128 analog signals by a hold trigger at their common peak point until they are serialized into a pair of differential outputs with the same time interval for channels and are read out. The differential outputs are amplified and converted into a signal with the height of the difference through two opamps.

The control and serial board are used to control VATA and to generate a trigger signal for flash ADC. They set the threshold of each channel and adjust the delay time from ored trigger of channels to a hold trigger. They are controlled by DAQ PC and need an interface board to be connected to VATA using a different logic signal type.

A analog output from VA Hybrid is digitized in 12 bit 64 MHz flash ADC[3] during a certain gate time which is initiated by the trigger from the control board and last for 128 time intervals

To see the noise of electronics itself, we measure its pedestal using the setup without the sensor in Fig2.

# $\begin{array}{c} \textbf{Channel vs. Sigma} \\ \hline 18 \\ \hline 18 \\ \hline 14 \\ \hline 12 \\ \hline 10 \\ \hline 8 \\ 6 \\ 4 \\ 2 \\ 0 \\ 0 \\ 20 \\ 40 \\ 60 \\ 80 \\ 100 \\ 120 \\ \hline \end{array}$

Fig 3. The preliminary pedestal test. The red and blue represent the sigma of pedestal in 128 channels of each VATA chip respectively

The average sigma is about 15ADC counts in the preliminary test of Fig 3. However, there is a room to improve because a VATA chip has two optional registers to compensate the incoming current to the pre-amplifier[4] by which the pedestal level can be reduced.

# 4. Summary

We fabricated the silicon array sensor of 4x64 pixels with the area of  $200x200(\mu m^2)$  to give two dimensional positions of X-rays which pass through. The leakage current in the sensor is less than 1.7nA at 70V. The front-electronics was set up to get a serially digitized output of 256 channels. The preliminary pedestal of electronics is about 15ADC and more tests are in progress to reduce the pedestal noise. To optimize the signal-to-noise, we will measure the different gains of the electronics channels using a charge pulse of 21.6fC injected as the most probable input of the electronics.

Finally we will show the optimized S/N and imaging test.

# REFERENCES

- [1] G. Lutz, Semiconductor Radiation Detector, Springer, New York, pp. 100-102, 1999.

- [2] Va1Ta\_3 Datasheet V0R1, http://www.ideas.no.

- [3] FADC64 firmware, http://www.noticekorea.com.

- [4] p.12 of [2]