# Design Verification Enhancement of FPGA-based PPS Trip Logics for Nuclear Power Plant

### Authors:

### Ibrahim Ahmed and Gyunyoung Heo (KHU) Jaecheon Jung (KINGS)

### Presented By Ibrahim Ahmed

Department of Nuclear Engineering, Kyung Hee University, Suwon, Republic of Korea

2016 KNS Spring Meeting

May 11-13, 2016

### **OUTLINES**

## INTRODUCTION

- NPP (nuclear power plant) is design to have a safe plant operation throughout the plant design life time.

- ✤ Many safety systems are incorporated into NPP to achieve this crucial goal.

- ✤ Among these systems is I&C systems which coordinates the activities of the plant during normal and abnormal plant operation.

- ✤ I&C systems monitor, control and protect the activities and status of the plant condition, and making decisions base on the design.

- The safety critical part of I&C systems is plant protection system (PPS).

- The primary objective of PPS is to protect and provide a reliable and rapid reactor trip if monitored parameters approach the specified limiting setpoints.

## INTRODUCTION

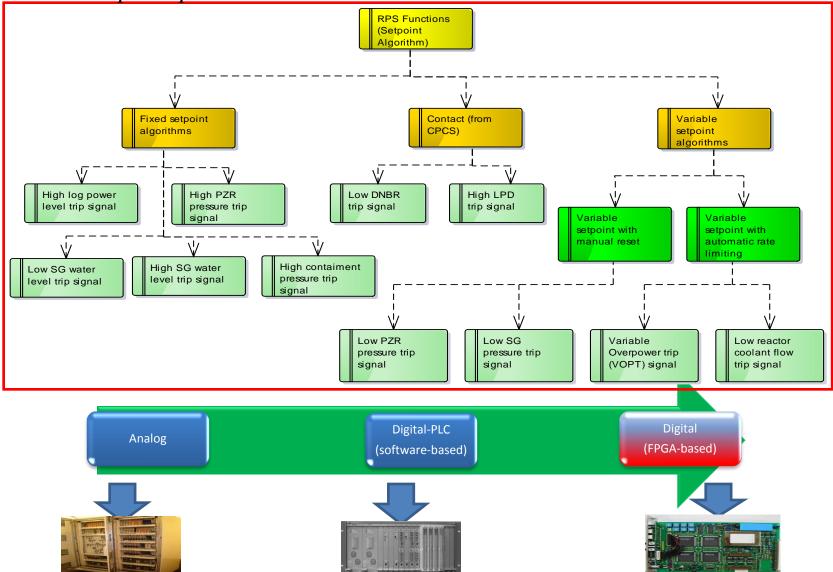

#### PPS plant parameters selected to be monitored.

Transition of I&C systems in NPP

• Design Requirements

\* <u>Requirement - Regulations</u>

- **10CFR50 Appendix A**, GDCs 13, 20, 21, 22, 23

- **RG 1.152** Criteria for Digital Computers in Safety Systems of Nuclear Power Plants

- **RG 1.153** Criteria for Safety Systems

Standards

- **IEEE 7-4.3.2** IEEE Standard Criteria for Digital Computers in Safety Systems of Nuclear Power Generating Stations

- **IEEE 603 1991** Criteria for Safety Systems for Nuclear Power Generating Stations

- IEC 62566 Nuclear power plants Instrumentation and control important to safety Development of HDL-programmed integrated circuits for systems performing category A functions, 2012.

#### • Design Requirements

\* <u>Requirements – Functional</u>

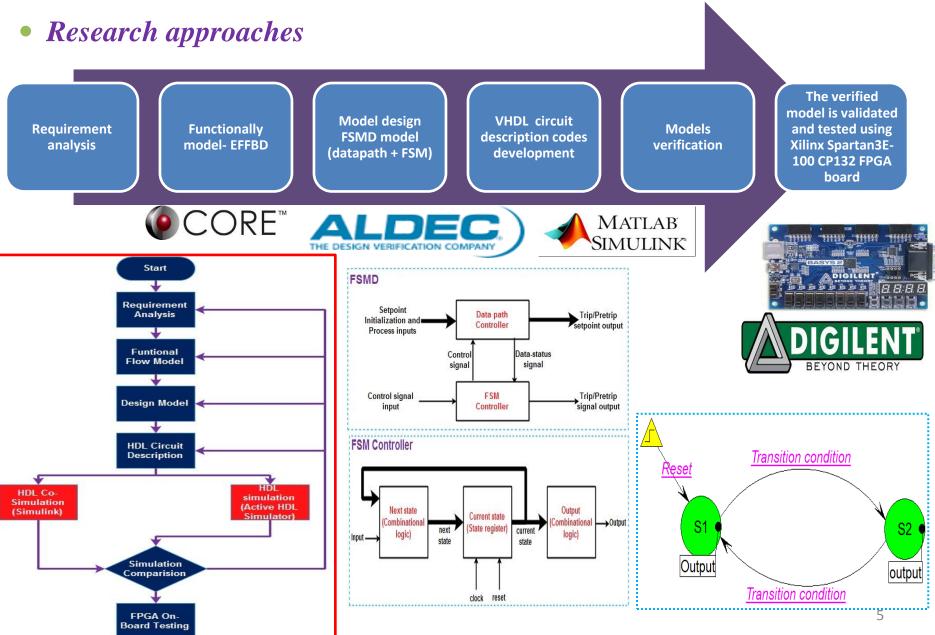

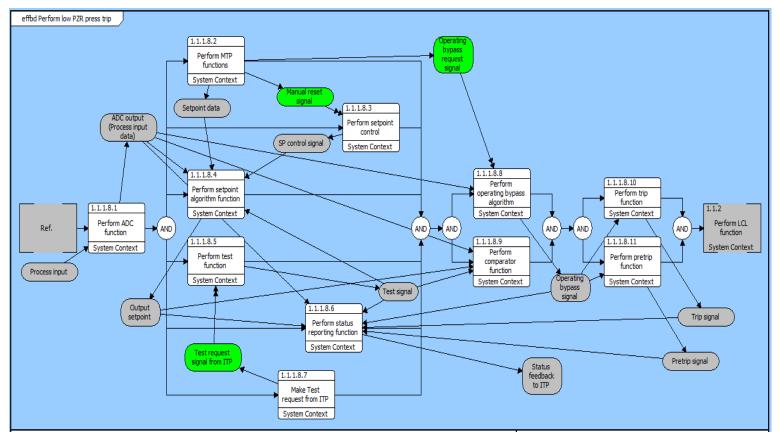

• EFFBD Model

\* Functional flow verification of the BP logic block diagram

• Vitech's CORE® Model Based Systems engineering software tool is used to developed EFFBD

EFFBD (enhanced functional flow block diagram) model for LPPT.

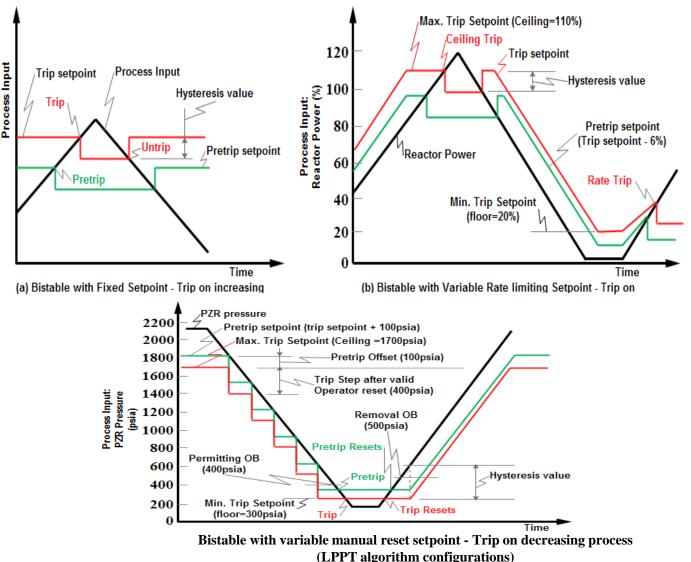

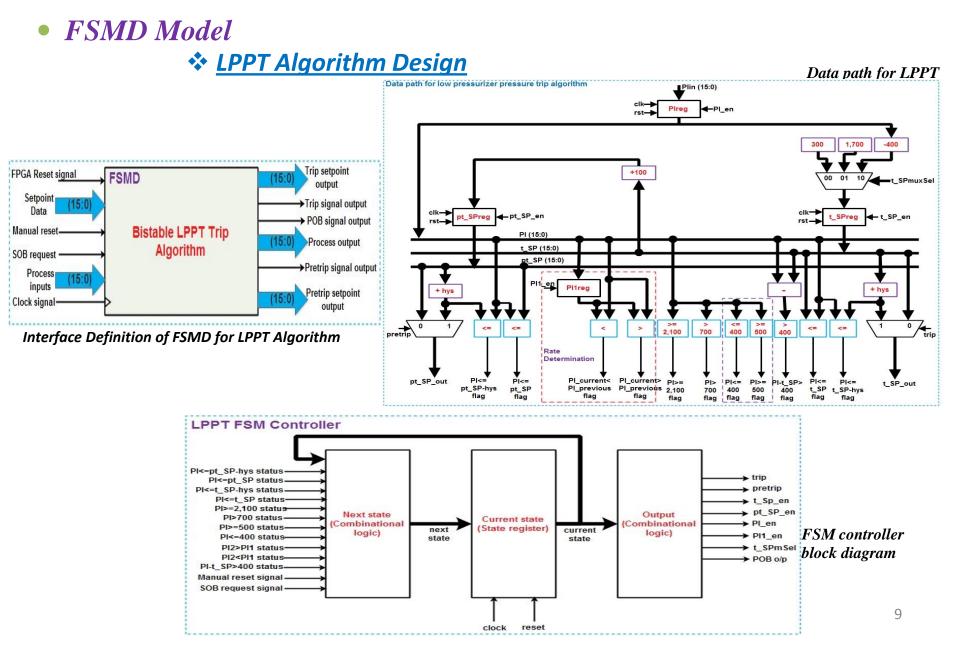

FSMD Model

\* LPPT Algorithm Design

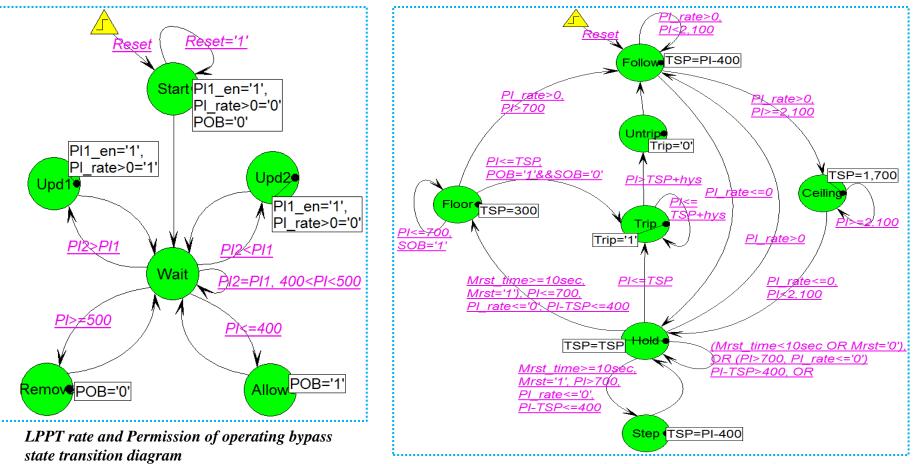

LPPT State transition diagrams

LPPT trip setpoint calculation state transition diagram

#### • FSMD Model

#### \* LPPT algorithm design

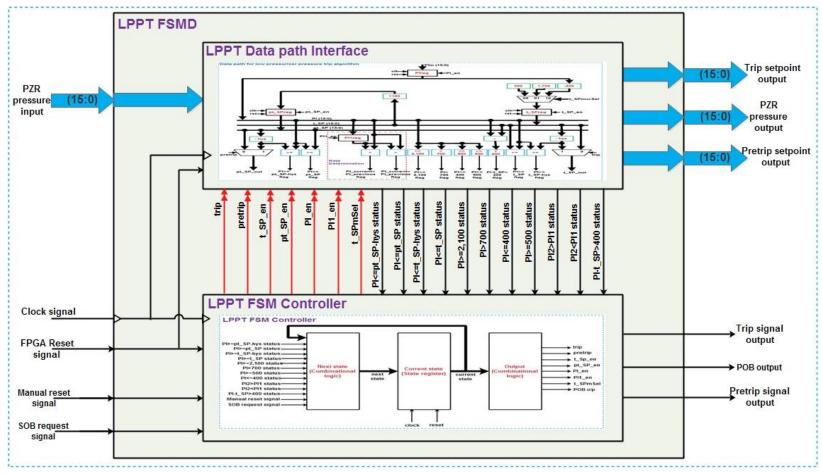

FSMD final design for LPPT configuration

### • VHDL coding, and Design Verification and Validation

Cosim FixedSP File Edit View Simulation Format Tools Help 🗋 🚅 🖬 🚳 👗 🖻 💼 (수 수 수 ! 으 으 ! 🕨 🔳 🗍 💽 🖳 🏭 🕅 🆃 🕮 📘 🖬 Normal ACTIVE-HDL Active-HDL Co-Sim trip SP +++ ++ lod ++++++ retrip\_SF Clock Pulse Generator eset FSM DATAPATH PI ou ACTIVE-HDL<sup>TI</sup> Reset Scope pretrip HDL Black-Box Process Input 100% FixedStepDiscrete Ready

Simulink co-simulation model for fixed setpoint algorithm

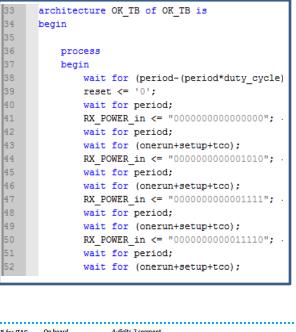

#### Test bench Code using VHDL

### • Fixed Setpoint Simulation Result: High SGWL trip

| Signal name                 | Value | ····?·································                                  |

|-----------------------------|-------|-------------------------------------------------------------------------|

| nr clock                    | 0     |                                                                         |

| reset                       | 0     |                                                                         |

| ⊯r start                    | 0     |                                                                         |

| ⊞ # SGWL_in                 | 40    | 0 \ 20 \ 60 \ 80 \ 85 \ 70 \ 60 \ 75 \ 80 \ 90 \ 95 \ 80 \ 90 \ 75 \ 40 |

| ⊞ # HSGWL_trip_SP           | 90    | 90                                                                      |

| <b>⊞ #</b> HSGWL_pretrip_SP | 75    | 75                                                                      |

| ⊞ # HSGWL_trip_SPc          | 90    | 0 χ 85 χ 90 χ 85 χ 90                                                   |

| ⊞ # HSGWL_pretrip_SPc       | 75    | 0 X 75 X 70 X 75 X 70 X                                                 |

| ⊞ # SGWL_out                | 40    | 0 \ 20 \ 60 \ 80 \ 85 \ 70 \ 60 \ 75 \ 80 \ 90 \ 95 \ 80 \ 90 \ 75 \ 40 |

| # trip                      | 0     |                                                                         |

| # pretrip                   | 0     |                                                                         |

Fixed setpoint, steam generator water level trip simulation result from Active HDL simulator

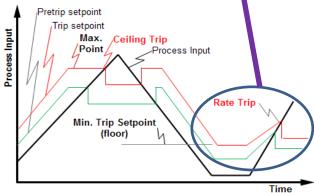

### • VOPT Simulation Result: rate trip

| Signal name               | Value | · · · · 200 · · · · 400 · · · · 600 · · · · 800 · · · · 1000 · · · · 1200 · · · · 1400 · · · · 1600 · · · · 1800 · · · · 2000 · · |

|---------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| nr clock                  | 1     |                                                                                                                                   |

| ⊯ reset                   | 0     | Change in R_power greater than 11%                                                                                                |

| ⊞ # RX_POWER_in           | 120   | 0 <u>10 20 30 50 70 90 110 120 90 80 70 50 20 0 10 20</u>                                                                         |

| <b>⊞ #</b> trip_SPc       | 105   | <u>(20 ) 25 ) 35 ) 45 ) 65 ) 76 ) 60 ) 76 ) 35 ) (20 ) 25 ) 35</u>                                                                |

| <b>⊞ #</b> pretrip_SPc    | 99    | <u>(14 ) (19 ) 29 ) 39 ) 59 ) 70 ) 54 ) ( ) 29 ) (14 ) 19 ) 29</u>                                                                |

| <b>⊞ n</b> r RX_POWER_out | 120   | <u>0 10 20 30 50 70 90 110 120 90 80 70 50 20 70 10 10 20</u>                                                                     |

| 🛚 trip                    | 1     |                                                                                                                                   |

| 🛚 pretrip                 | 1     |                                                                                                                                   |

|                           |       | VOPT rate trip simulation result                                                                                                  |

|                           |       | Pretrip setpoint                                                                                                                  |

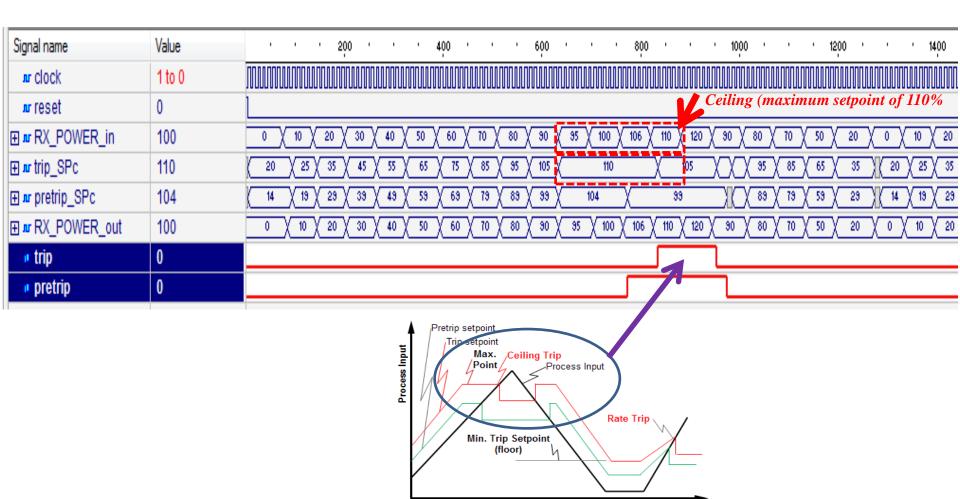

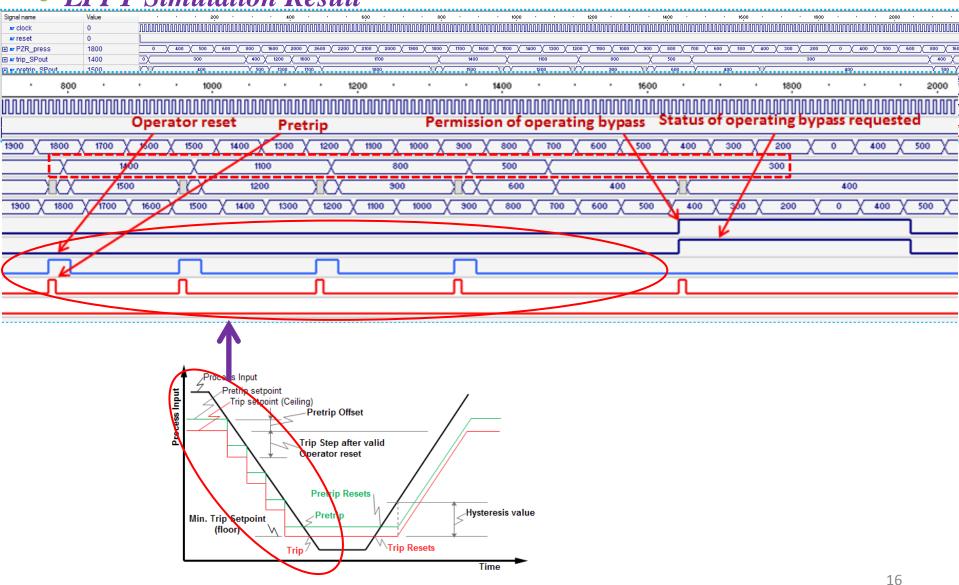

### • VOPT Simulation Result: Ceiling trip

Time

#### • LPPT Simulation Result

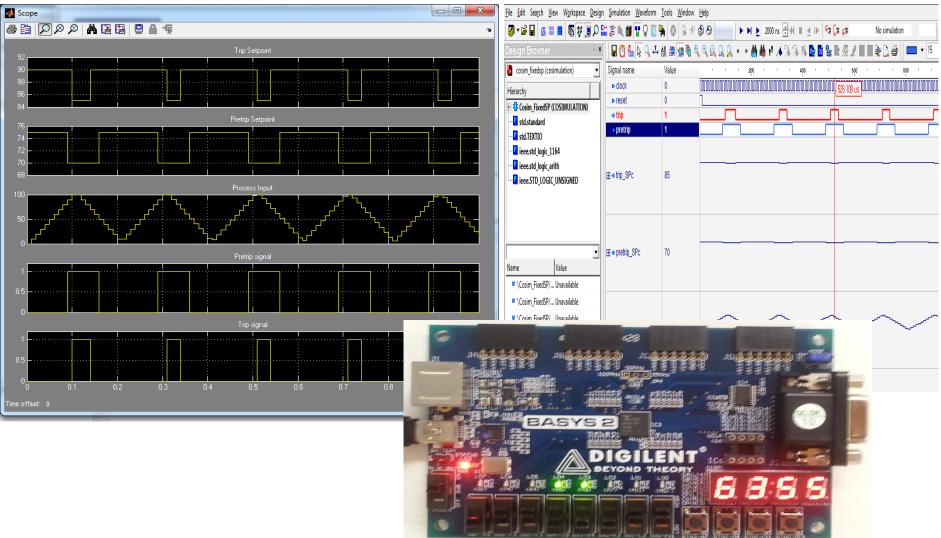

#### • Simulink Co-simulation Result for fixed setpoint

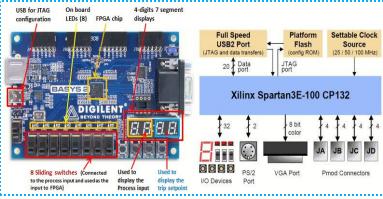

#### **On-board testing**

## CONCLUSION

- The PPS trip logic functions are designed, modeled, developed, verified, and validated in this work.

- The VHDL code is developed for each algorithm and the developed VHDL codes are verified and tested using Active-HDL tool.

- To further enhanced the design verification, an HDL Co-Simulation with MATLAB/SIMULINK is performed. It provides additional verification method for HDL design.

- ✤ To validate the design, the FPGA device is configured and tested. It operates without using the operating system or application software.

- Therefore, it can be concluded that, using the model-based approaches demonstrated in this work, together with co-simulation can enhanced the design verification as well as provides easy and quick HDL design verification.

# Thank you

for

# your attention